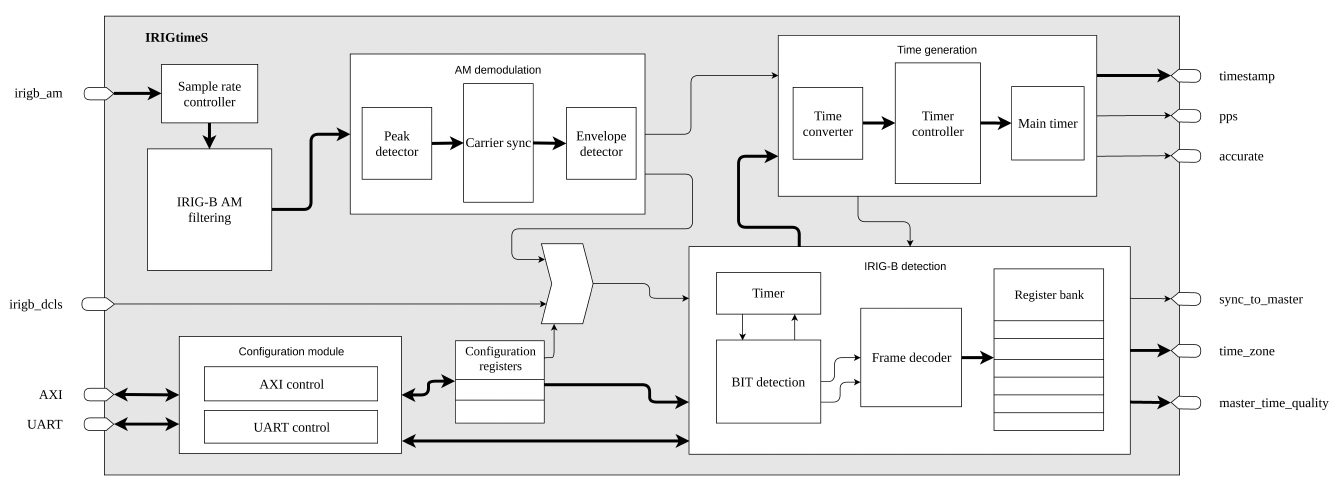

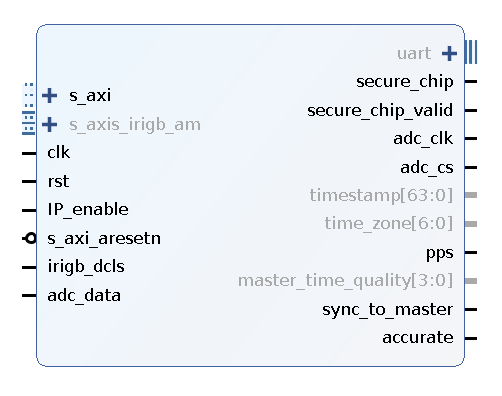

IRIGtimeS implements an IRIG 200-04 compliant time synchronization slave on FPGA devices. This IRIG-B slave IP has been designed to support all the IRIG-B coded expressions as well as DCLS and AM modulations in order to provide maximum flexibility.

This IRIG-B slave IP receives IRIG-B frames each second, getting the time information (seconds, minutes, hours, days, years, control functions and binary straight seconds) depending on the IRIG-B time code. This IP implements a 64-bit internal timer in order to provide the timestamp (in seconds) and nanoseconds value. This timer is synchronized in value and frequency with the received IRIG-B time information. This IP has been designed to provide autonomous operation, requiring as less con

figuration as possible.

IRIGtimeS is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+(Zynq MPSoC, Kintex, Virtex)

- Versal

- Managed Ethernet Switch IP Core for Xilinx Vivado Tool -

It is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

IRIGtimeS key features

- IRIG 200-04 compliant time synchronization slave

- Support for DCLS and AM modulations

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds

- Sub-microsecond synchronization with the IRIG-B master

- 64-bit internal timer synchronized in time and frequency with the IRIG-B master

- 32-bit for timestamp in seconds and 32-bit for nanoseconds

- Periodic pulse output for testing

IRIGtimeS IP core block diagram is represented in the following figure:

Supported boards for the Reference Designs

- SoC-e SMARTzynq brick (Recommended)

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.