Multiple TSN IP Core: Generate the TSN bridge or end-point optimized for your application

Time Sensitive Networking (TSN) is the name of the IEEE 802.1 Task Group responsible for standards at Data Link Layer. This group provides the specifications that will allow time-synchronized and low latency streaming services through IEEE 802 networks. This set of protocols, deliver streams with guaranteed bandwidth and dterministic latency.

TSN is constantly evolving and it is targeting different sectors, like Automotive, Broadcasting or Aerospace. Therefore, this flexibility and reconfiguration can be only achieved through reconfigurable logic like FPGAs, HDL IPs and embedded software.

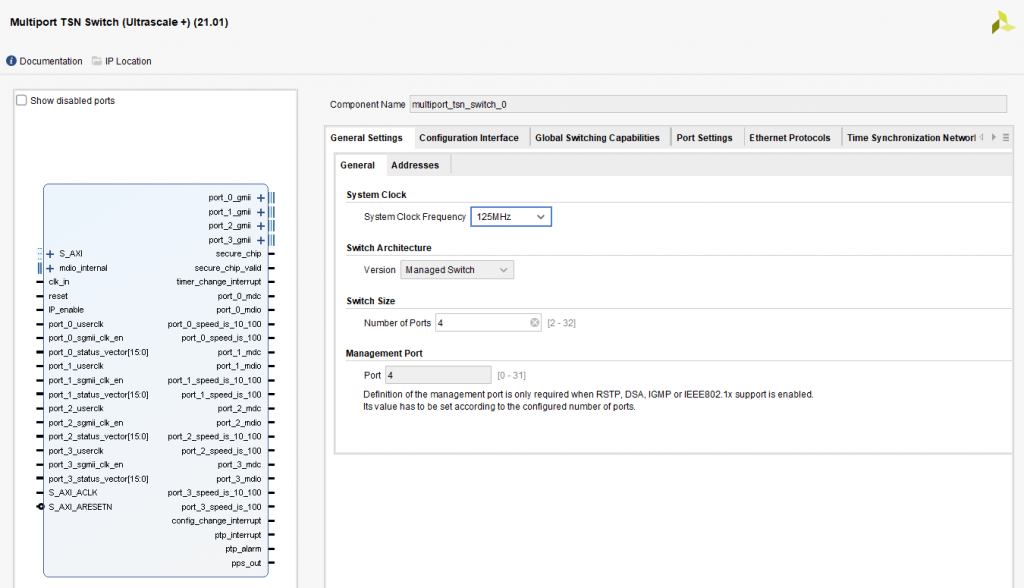

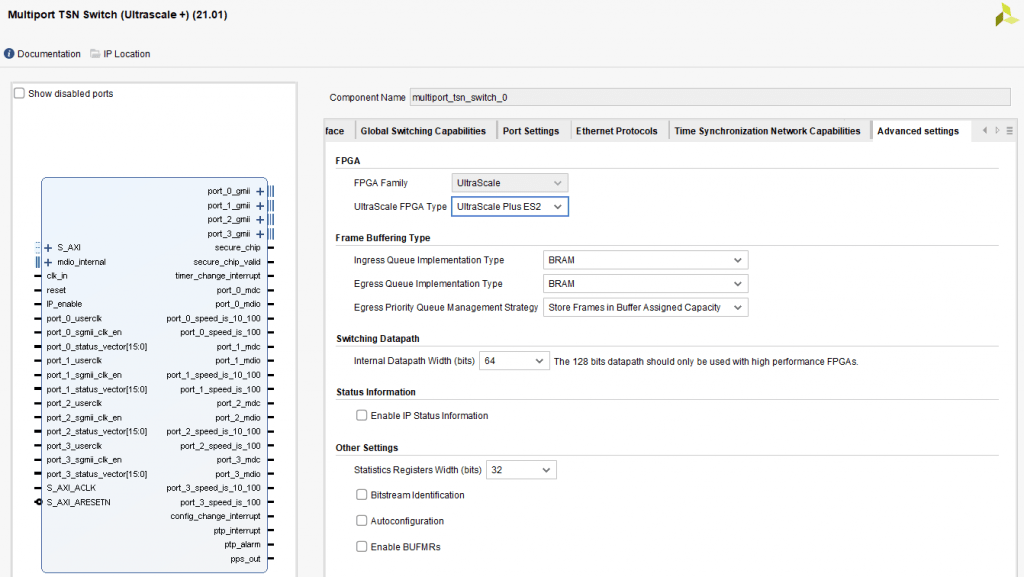

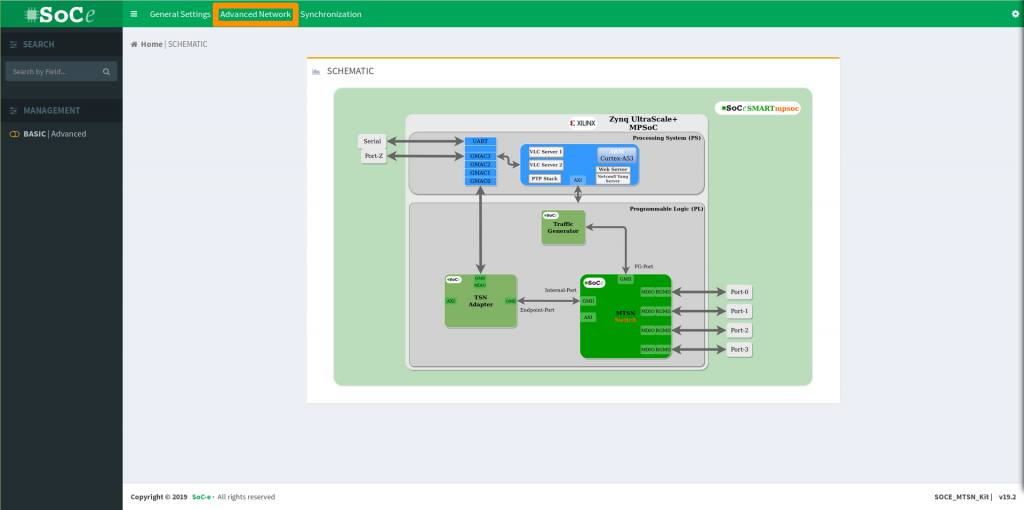

Our Multiport Time Sensitive Networking (MTSN) Switch IP core is a flexible HDL code ready to generate TSN end-point or bridge implementations. This IP Core is provided with a rich set of Generic parameters in order to obtain the best functionalities resources trade-off. This configuration of the TSN IP Core can be done through the Vivado GUI.

MTSN Switch IP Core key features

Interfaces

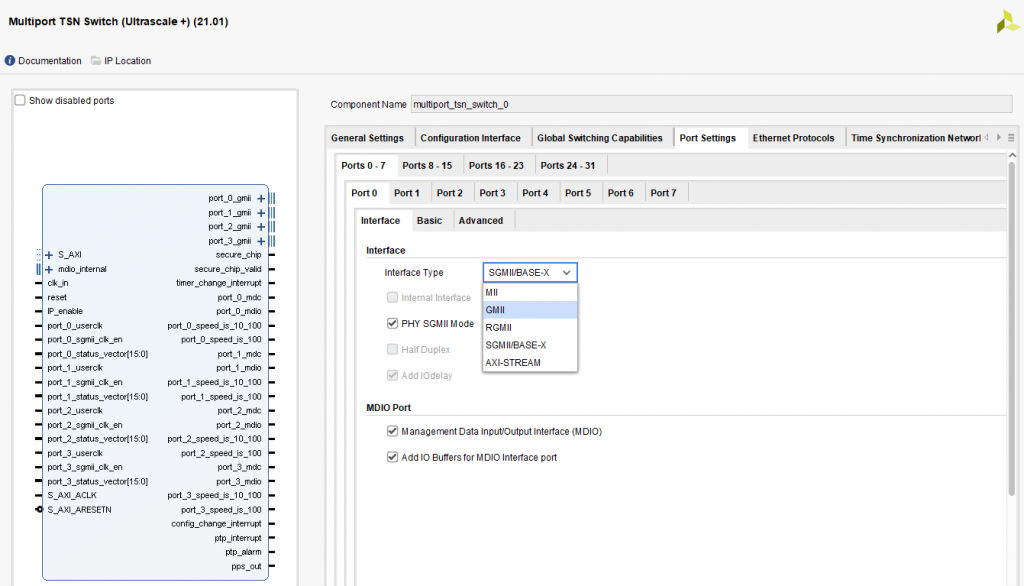

- Full-duplex 10/100/1000 Mbps Ethernet Interfaces

- Configurable up-to 32 Ethernet ports

- MII/RMII/GMII/RGMII/SGMII/QSGMII Physical Layer device (PHY) interfaces

- Different data rate supported for each port

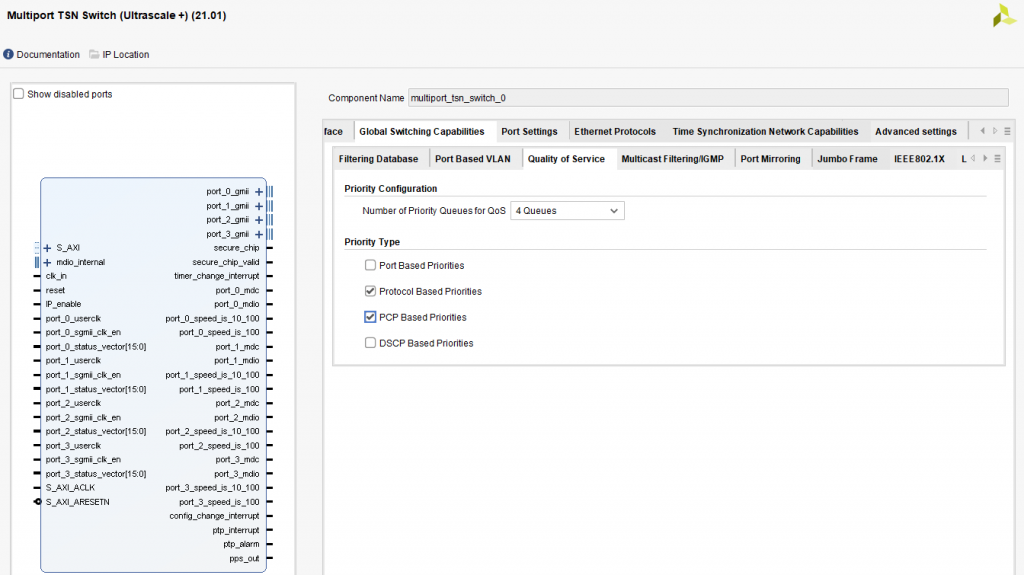

Switching

- Dynamic MAC Table with automatic MAC addresses learning and aging

- Static MAC Table

- Jumbo Frame Management

- Broadcast/Multicast Storm Protection

- Per-Port Rate limiting (Broadcast, Multicast and Unicast traffic)

- Port-based VLAN support

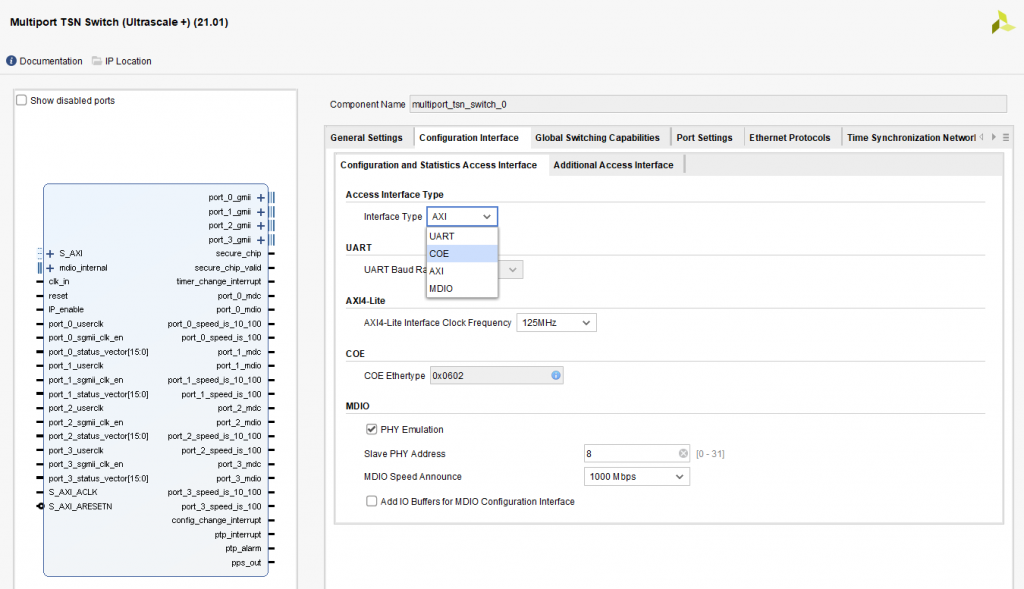

Low Level Configuration

- MDIO, UART, AXI4-lite or CoE management interfaces

- Configuration-over-Ethernet (CoE): Full access to internal registers through the same Ethernet link that connects to the CPU

- Drivers are provided with IP Core purchase

High Level Configuration

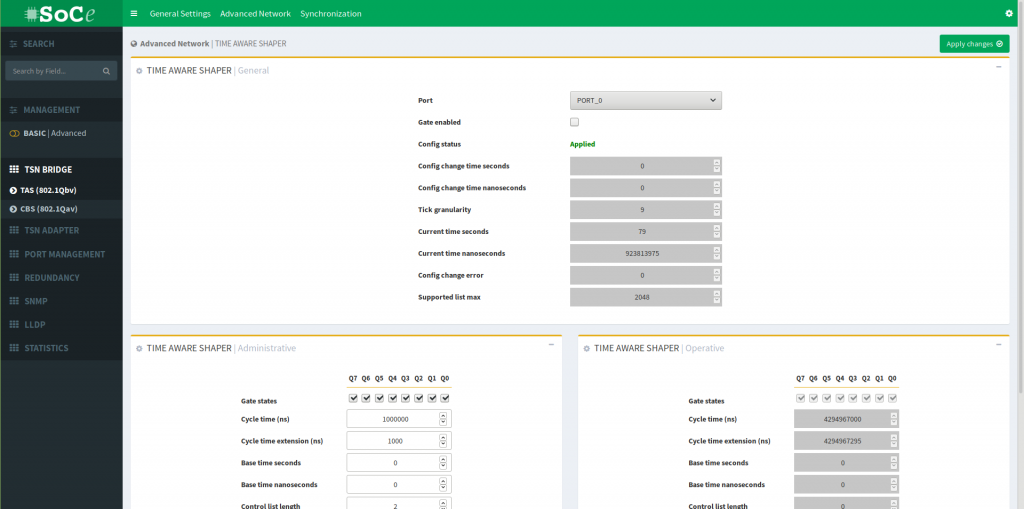

- RESTCONF/NETCONF YANG model support (CNC configuration)

- High-level Configuration GUI

Time-Sensitive Networking

- IEEE 802.1AS for Time Synchronization Layer

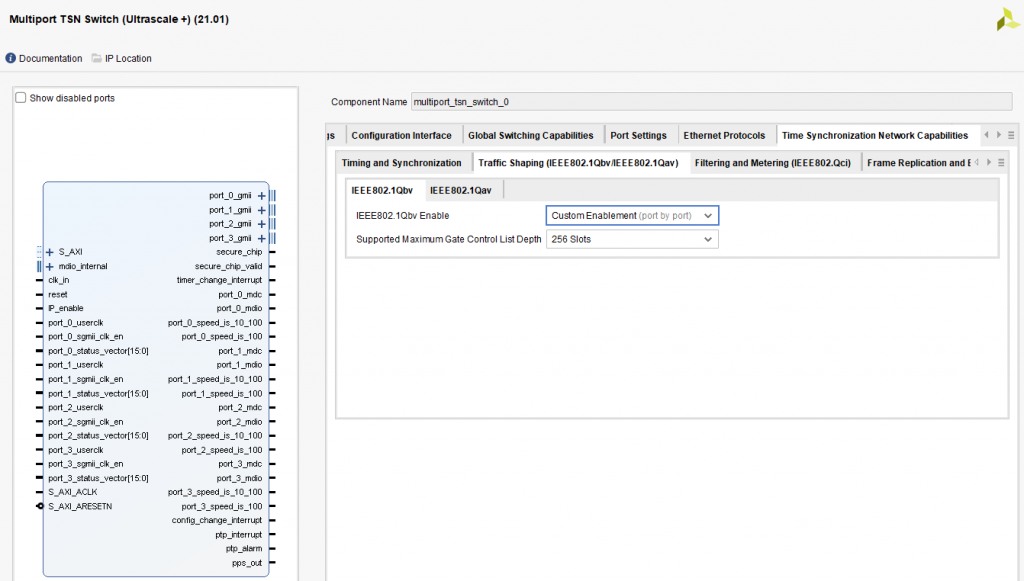

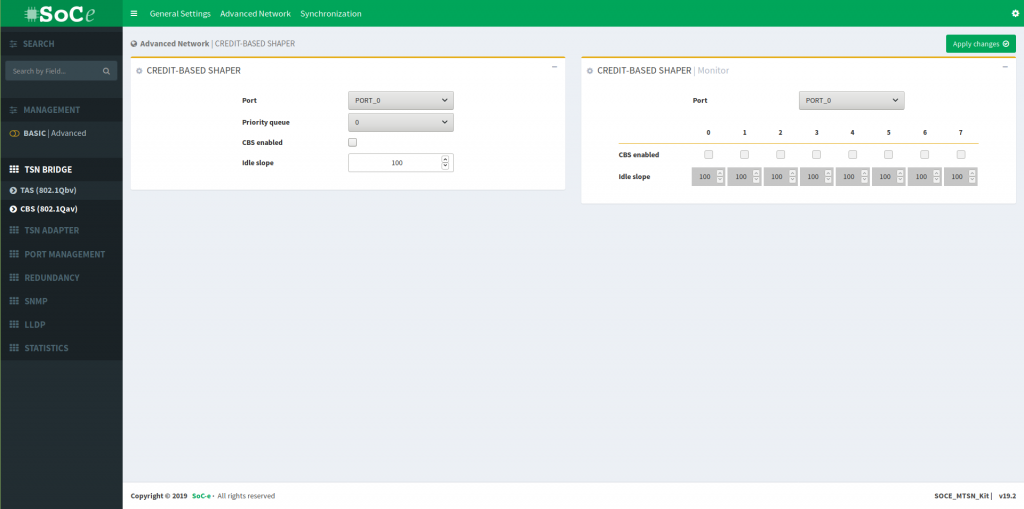

- IEEE 802.1Qav for Reserved Traffic

- Credit Based Shaper: Configurable bandwidth reservation for each traffic class

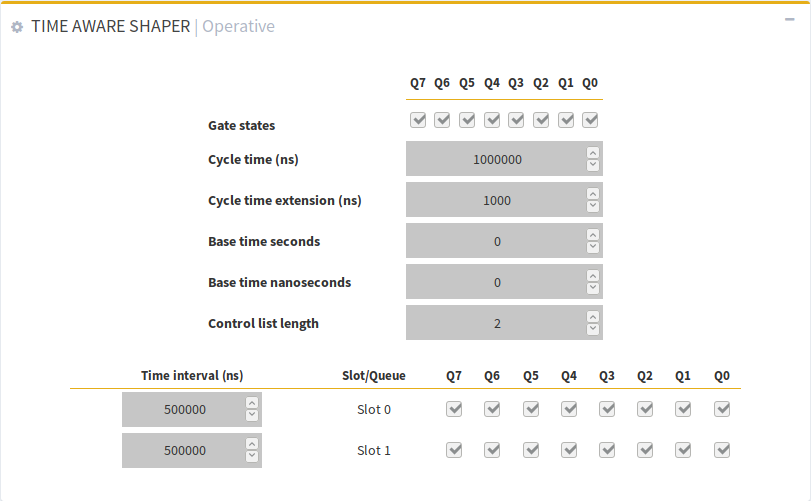

- IEEE 802.1Qbv for Scheduled Traffic

- Time Aware Shaper: Configurable number of time slots

- IEEE 802.1Qcc for Network Management

- NETCONF for managing YANG data

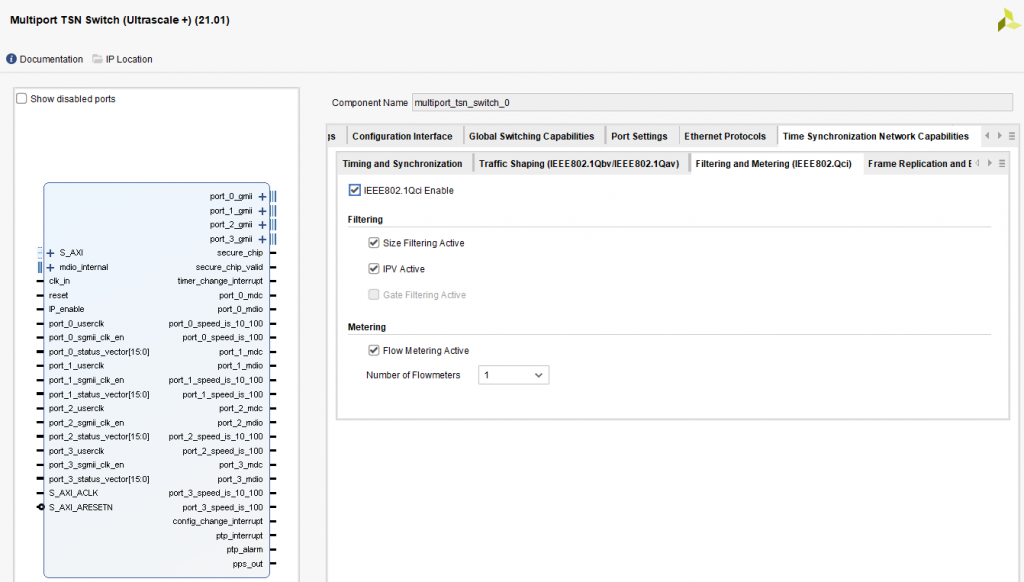

- IEEE 802.1Qci for Stream Filtering and Policing

- IEEE 802.1AB for LLDP (Link Layer Discovery Protocol)

- IEEE 802.1w for Rapid Spanning Tree Protocol

- IEEE 802.1s for Multiple Spanning Tree Protocol

- IEEE 802.1CB for Frame Replication and Elimination for Reliability

- IEEE 802.1Qbu/802.3br for Frame Preemption

- Cut-Through support for Isochronous Scheduled Traffic (*)

*: Future Release and/or Interoperability Test pending.

Supported Xilinx FPGA Families and Evaluation boards

Our MTSN IP Core can be deployed in the following Xilinx families. You can find the different Xilinx product tables and selection guides at the following links:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

In SoC-e we also develop Networking System-on-Modules or Networking SoMs. In this case, we have the MTSN Kit solution for any customer that requires an all-in-one solution to introduce Time Sensitive Networking in their equipment.