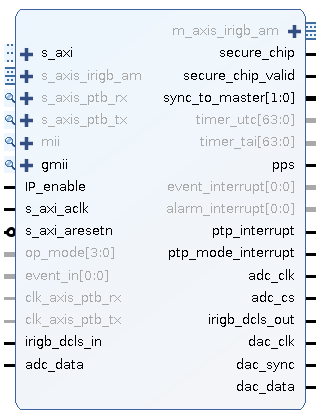

MULTIsync IP Core is a multi-protocol redundant time synchronization core that provides sub-microsecond time synchronization, providing maximum flexibility for every scenario. It is able to provide time synchronization using IEEE 1588-2008 (PTPv2) and IRIG-B time synchronization protocols.

MULTIsync IP Core supports the following synchronization input sources:

- PTP: Ethernet. PTP Slave at the input

- IRIG-B: IRIG-B compliant signal. IRIG-B Slave at the input

- Free Running Timer: Digital input

MULTIsync IP Core supports the following synchronization output options:

- PTP: Ethernet. PTP master at the output

- IRIG-B: IRIG-B compliant signal. IRIG-B Slave at the output

- Free Running Timer: Digital Output

This versatility enables different cases-of-use for MULTIsync that are complementary:

- It can provide time synchronization redundancy, making possible to connect the IP to a PTP network and to an IRIG-B master at the same time. The user is able to select which is the time source used between the three available ones (PTP, IRIG-B, free running timer)

- It can act as a PTP to IRIG-B or IRIG-B to PTP bridge while the IP is synchronized with the selected master

- It can act a PTP or IRIG-B grandmaster

MULTIsync can be used in combination with SoC-e HSR-PRPSwitch, TSNSwitch, UnmanagedEthernetSwitch or ManagedEthernetSwitch IP cores to introduce Ethernet traffic switching capabilities or HSR and PRP redundancy.

MULTIsync is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

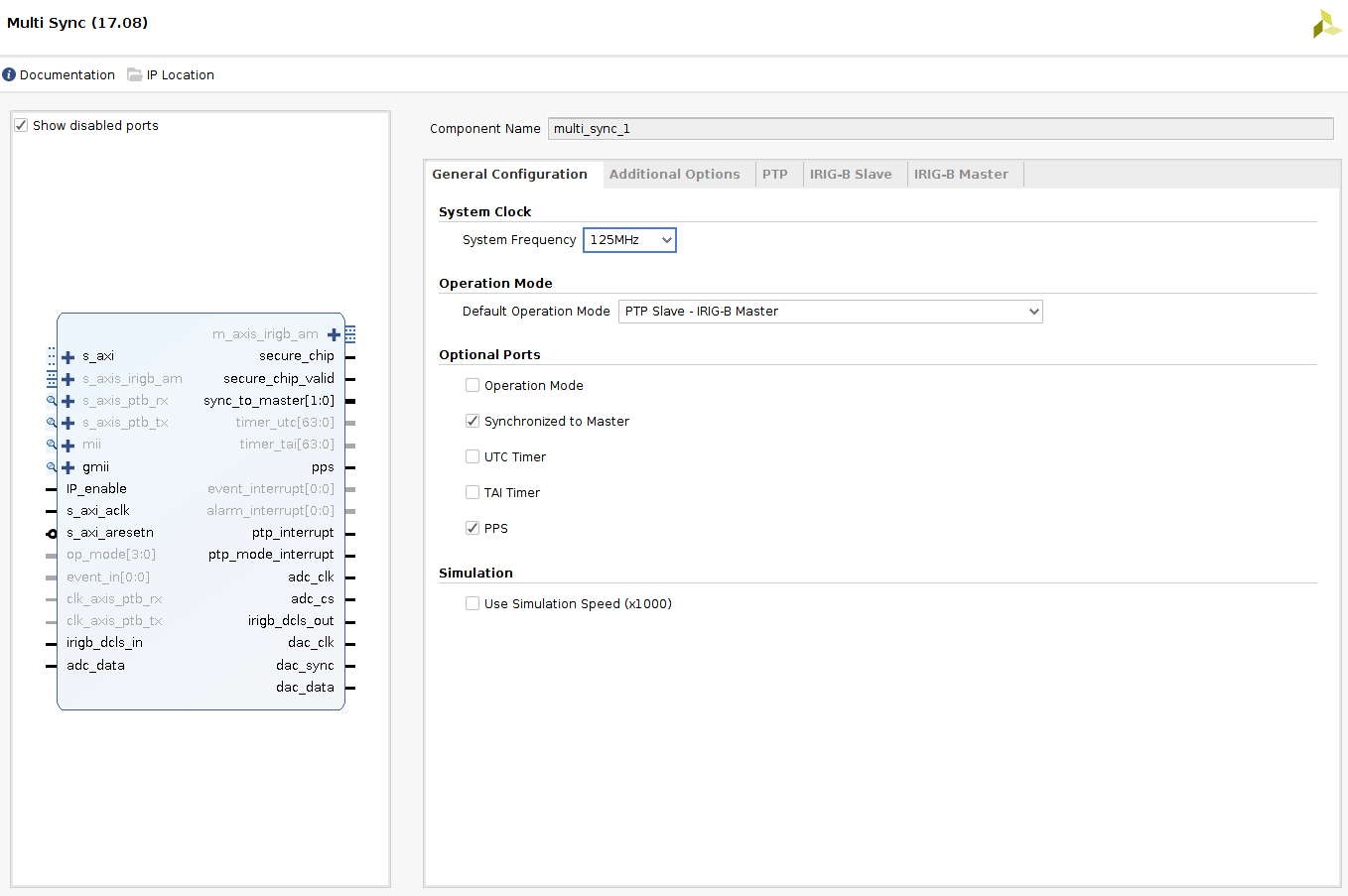

MULTIsync is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

MULTIsync IP Core main features:

- Multi-protocol redundant time synchronization.

- IEEE 1588-2008 (PTPv2) and IRIG-B time synchronization protocols supported simultaneously.

- 12 different operation modes.

- 3 independent 64-bit adjustable timers associated to each slave. (32 bit sub-nanosecond frequency adjust.

- One Pulse Per Second Output available.

- Event timestamping supported (up to 4 different events simultaneously).

- Alarm detection supported (up to 4 different alarms simultaneously).

PTP Features

- 10/100/1000 Mbps Ethernet operation supported.

- AXI-S interface supported:

- 1 Gigabit Ethernet: 8-bit data width.

- 10 Gigabit Ethernet: 64-bit data width.

- Selection if the Ethernet frame includes the preamble or not.

- 16 position FIFO depth. Old timestamp values are stored for avoiding overrun.

- End-to-End and Peer-to-Peer delay mechanisms support.

- Support for PTP on both, Layer 2 (Ethernet) and Layer 3 (IPv4) interfaces.

- Support VLAN tagged PTP messages.

- IEEE1588 Profiles: Default, Power, Power-Utility (IEC61850-9-3), AS.

IRIG-B Slave Features

- Support for DCLS and AM modulations.

- Internal filtering of the AM signal.

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds.

- IEEE-1344 extension support.

- Input type (IRIG-B time code) confi gurable both before implementation and on the fly.

- Implements a generic ADC controller compatible with SPI, QSPI and MICROWIRE protocols.

IRIG-B Master Features

- Support for DCLS and AM modulations.

- Support for all IRIG-B coded expressions, including year information, control functions and straight binary seconds.

- IEEE1344 extension support.

- Output type (IRIG-B time code) confi gurable both before implementation and on the fly.

- Implements a generic DAC controller compatible with SPI, QSPI and MICROWIRE protocols.

Free Running Timer Features

- Fully managed by the user (time and frequency adjustment).

Supported boards for the Reference Designs:

- SoC-e SMARTzynq brick (Recommended)

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.