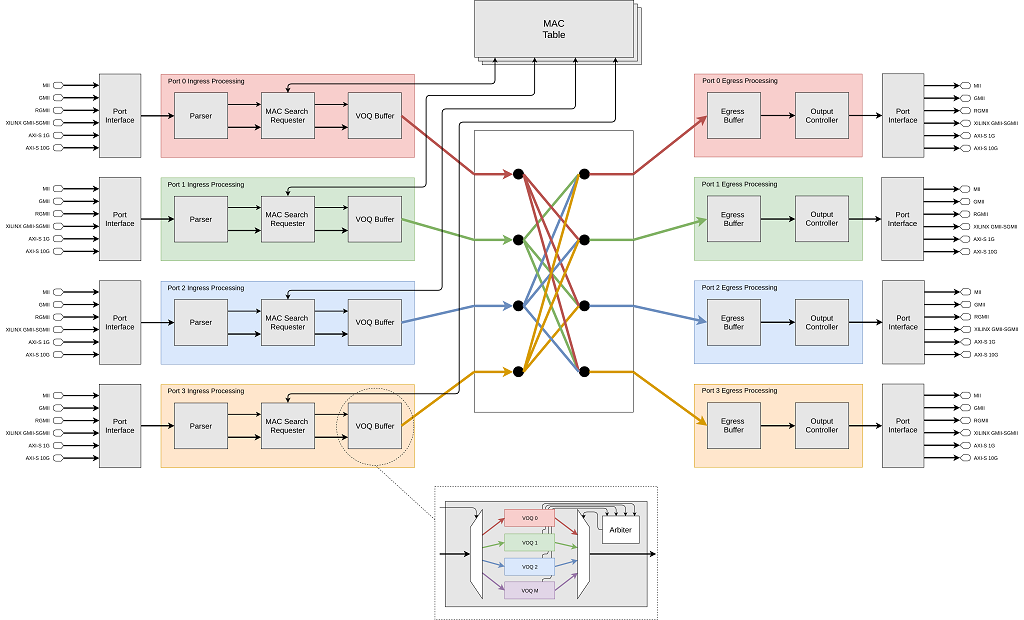

10G Managed Ethernet Switch (MES) IP core features a full-speed, Head-Of-Line effect free crossbar matrix that allows continuous transfers between all the ports. It supports up-to 32 ports with different line speed. The switch implements a Store & Forward switching approach to fulfill Ethernet standard policy regarding frame integrity checking.

10G Managed Ethernet Switch (MES) IP core features a full-speed, Head-Of-Line effect free crossbar matrix that allows continuous transfers between all the ports. It supports up-to 32 ports with different line speed. The switch implements a Store & Forward switching approach to fulfill Ethernet standard policy regarding frame integrity checking.

The internal micro-architecture includes disruptive enhancements in order to ensure a reliable operation of the switch even in critical use-cases. As an example, Virtual Output Queues combined with mirrored MAC tables allow simultaneous access to the matrix at maximum data throughput. The IP does not request any external memory.

10G MES is a multi-speed (100M/1G/2.5G/5G/10G s) switch IP and supports IEEE 1588 V2 Transparent Clock functionalities. This feature modifies PTP event messages taking into account the time spent crossing the switch. This scheme improves distribution accuracy by compensating delivery variability across the network. Specifically, 10G MESsupports IEEE 1588 V2 One Step Transparent Clock Peer-to-Peer (P2P) functionality by using independent hardware for each port. This feature allows compensating the residence time but also the delay of each link.

The IP includes MII/GMII/RGMII native interfaces for Ethernet PHY devices and it can be combined with Xilinx IP to support RMII/SGMIIQ/SGMII and USXGMII among other interfaces. It also provides an AXI4-Stream interface to ease the connection to other IPs Cores like SAScrypt for wire-speed security.

- 10G Managed Ethernet Switch IP Core for Xilinx Vivado Tool -

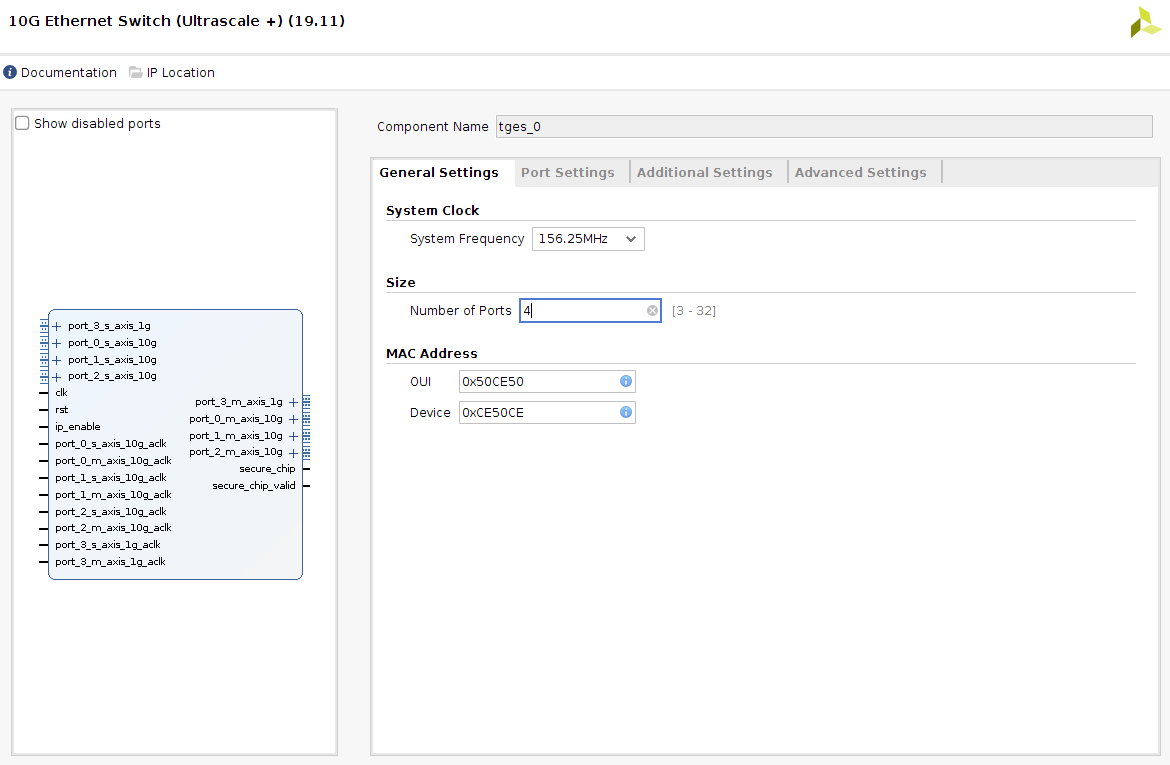

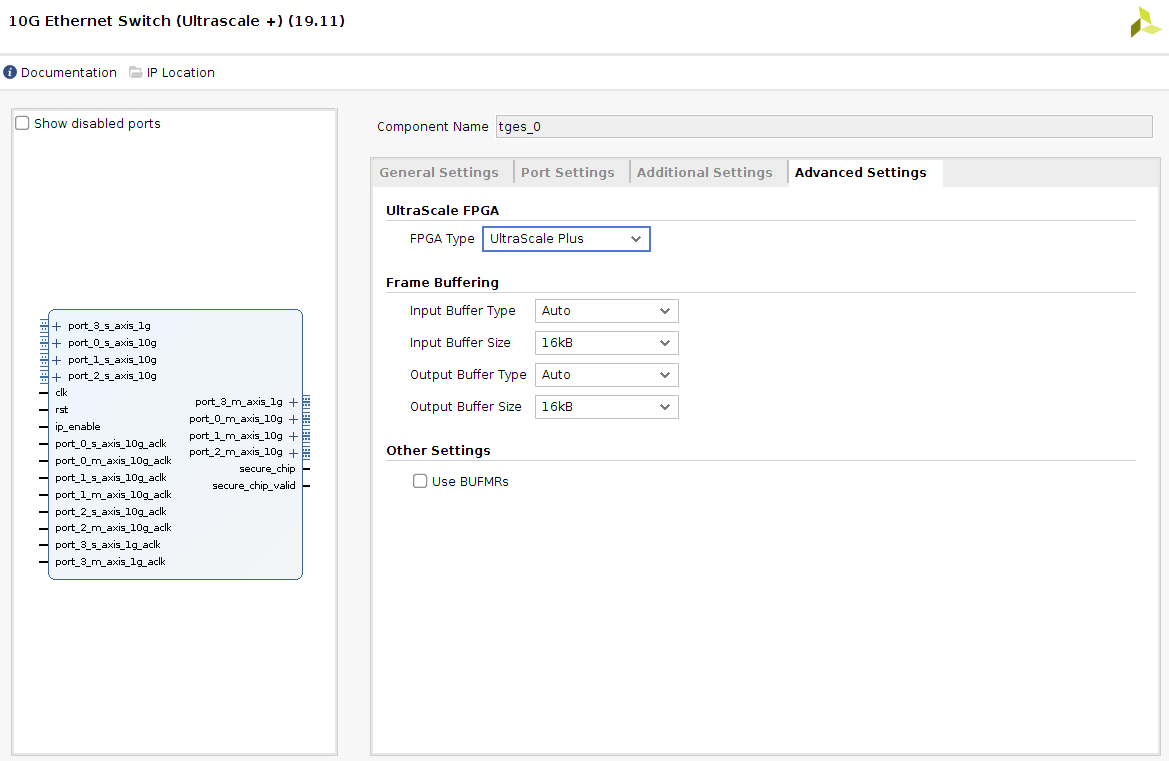

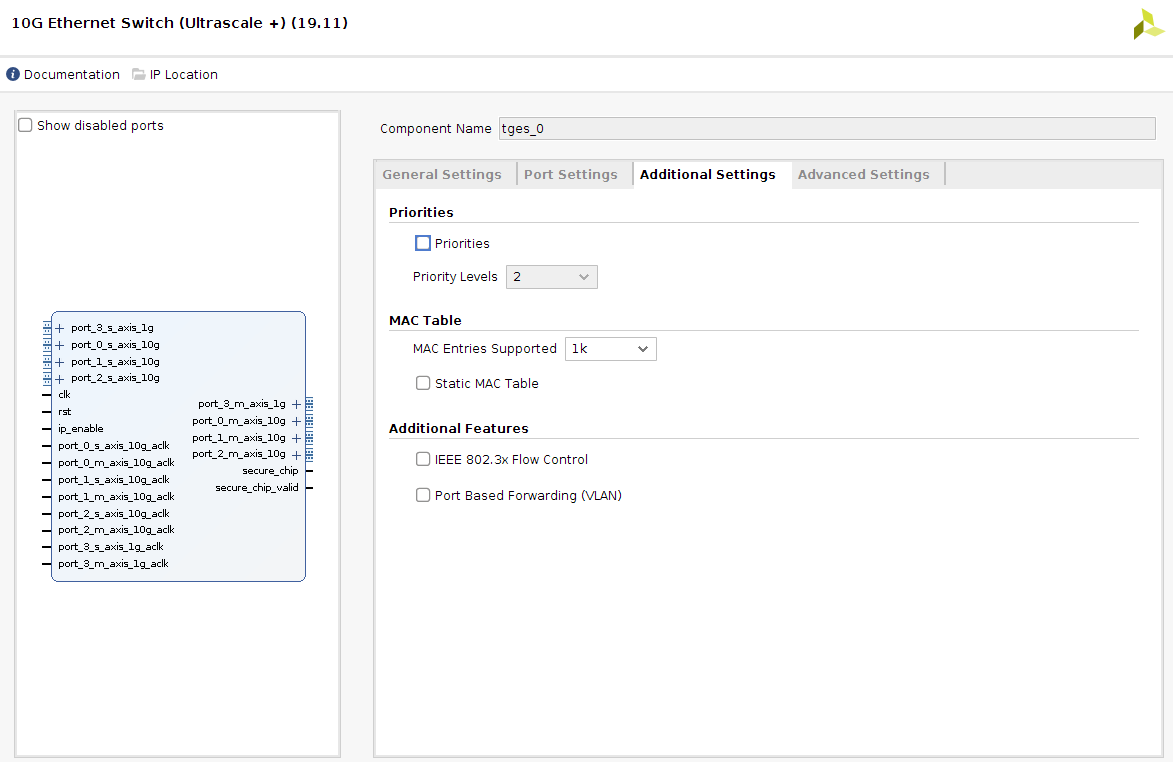

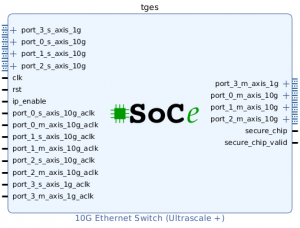

10G Managed Ethernet Switch IP is fully integrated on Xilinx Vivado IPI tool. This Graphical Interface allows configuring the generic parameters of the IP from a high-level point of view. Thanks to this flexibility at synthesis time, it is feasible obtaining an optimized implementation in terms of features and ports for a given application and device. Additionally, the IP can be instantiated directly using any HDL language.

10G Managed Ethernet Switch IP Core key features:

Interfaces

- Full-duplex 100M/1G/2.5G/5G/10G Ethernet Interfaces

- Configurable from 3 up-to 32 Ethernet ports

- MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII Physical Layer device (PHY) interfaces

- Different data rate supported for each port

- Copper and Fiber optic media interfaces: 100M/1G/2.5G/5GBase-T, 100MBase-FX, 1GBase-X, 10GBase-SR, 10GBase-LR, 10GBase-BX

Switching

- Dynamic MAC Table with automatic MAC addresses learning and aging

- Static MAC Table

- Jumbo Frame Management

- Ethertype Based Switching

- Port Mirroring

- Broadcast/Multicast Storm Protection

- Per-Port Rate limiting (Broadcast, Multicast and Unicast traffic)

Time Synchronization

- IEEE 1588v2 Stateless Transparent Clock functionality (P2P – Layer 2/ E2E – Layer 2)

- Compatible with SoC-e IEEE 1588 IP Cores (1588Tiny, PreciseTimeBasic)

Traffic Management

- Multicast Frame Filtering

- Switching Portmask: User-defined forwarding of frames to concrete ports

- Port-based VLAN support

- QoS

- Priorities (PCP-802.1p, DSCP TOS, Ethertype)

- IEEE 802.1X EAPOL hardware processing

- DSA (Distributed Switching Architecture) tagging: The ideal case for using DSA is when an Ethernet switch supports a “switch tag” , a hardware feature where the switch inserts a specific tag for each Ethernet frame it received to/from specific ports to help the management interface figure out:

- What port is this frame coming from

- What was the reason why this frame got forwarded

- How to send CPU originated traffic to specific ports

Configuration

- MDIO, UART, AXI4-Lite or CoE (Configuration-over-ethernet) management interfaces

- Configuration-over-Ethernet (COE): Full access to internal registers through the same Ethernet link that connects to the CPU

- Drivers are provided with IP Core purchase

Redundancy Protocols

- M/RSTP (Software stack required)

- Hardware support for M/RSTP

- Reference M/RSTP stack for Linux provided with the IP Core

- Posix Compatible RSTP stack available

Supported Xilinx FPGA Families and Evaluation boards

Our TGES IP Core can be deployed in the following Xilinx families. You can find the different Xilinx product tables and selection guides in the following links:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

When it comes to hardware platforms, at SoC-e we also develop System-on-Modules (SoMs) that can be provided with a preloaded design of our IP Cores. In this case, our SoMs are specially developed for Networking applications. We have SoMs based on 7-Series, Ultrascale or Ultrascale+ Xilinx FPGA Families.

For the case of our 10G Ethernet Switch, we recommend the following hardware:

- SoC-e 10G MES KIT: Xilinx ZU106 board; SFP+ cage FMC; 10G Fiber Optic SFP+; Fiber Optic bidirectional LC tails.

- For other development boards, we can provide an evaluation version time-limited IP Core.