1588Tiny is a IEEE1588-2008 V2 Slave Only hard-only compliant clock synchronization IP core for Xilinx FPGAs. It is focused on equipments that requires basic IEEE 1588 functionality using the minimum resources. 1588Tiny is capable of accurately time-stamping IEEE 1588 telegrams and also provides a synchronized clock using only hardware modules.

1588Tiny is a IEEE1588-2008 V2 Slave Only hard-only compliant clock synchronization IP core for Xilinx FPGAs. It is focused on equipments that requires basic IEEE 1588 functionality using the minimum resources. 1588Tiny is capable of accurately time-stamping IEEE 1588 telegrams and also provides a synchronized clock using only hardware modules.

An embedded processor is not required, nor a generic Ethernet MAC. 1588Tiny includes an optimized Ethernet MAC to process PTP frames. It supports Power Profile and IEC 61850 and it can also support other profiles.

1588Tiny is supported on the following Xilinx FPGA Families:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

- 1588Tiny IP Core for Xilinx Vivado Tool -

It is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

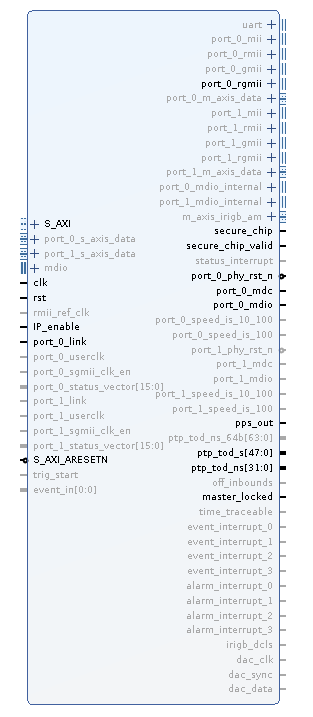

1588Tiny key features:

General

- Available for Vivado (IP Integrator)

- Single-port and Dual-port (the ethernet interface can be used for other purposes) modes supported

Interfaces

- MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII Physical Layer device (PHY) interfaces

- AXI-Stream interface supported

- 10/100/1000Mbps speeds supported

Time Synchronization

- Layer-2 PTP supported (Single-port and Dual-port)

- Layer-3 PTP supported (Single-port)

- Supported Profiles: Power Profi le, Utility Profile, IEC61850 profi le and default pro file

- Output Timer available: “64-bit nanosecond” or “48-bit second + 32-bit nanosecond”

- PPS output available

- Optional IRIG-B master output synchronized with the PTP internal timer (DCLS and AM modulations)

- Event timestamping supported

- Alarm detection supported

Supported boards for the Reference Designs:

- SoC-e SMARTzynq brick (Recommended)

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.