PreciseTimeBasic is a IEEE1588-2008 v2 compliant clock synchronization IP core for Xilinx FPGAs. It is capable of accurately time stamp IEEE 1588 telegrams and also to provide a compatible timer. All these processes are carried out by hardware modules.

PreciseTimeBasic is a IEEE1588-2008 v2 compliant clock synchronization IP core for Xilinx FPGAs. It is capable of accurately time stamp IEEE 1588 telegrams and also to provide a compatible timer. All these processes are carried out by hardware modules.

PreciseTimeBasic IP comprises different hardware and software elements:

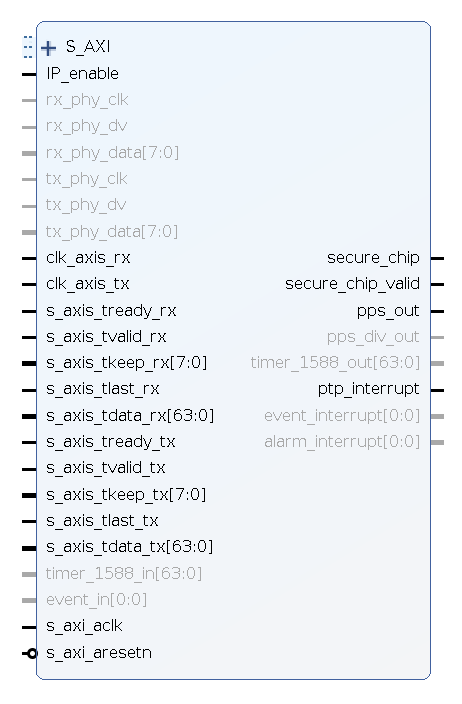

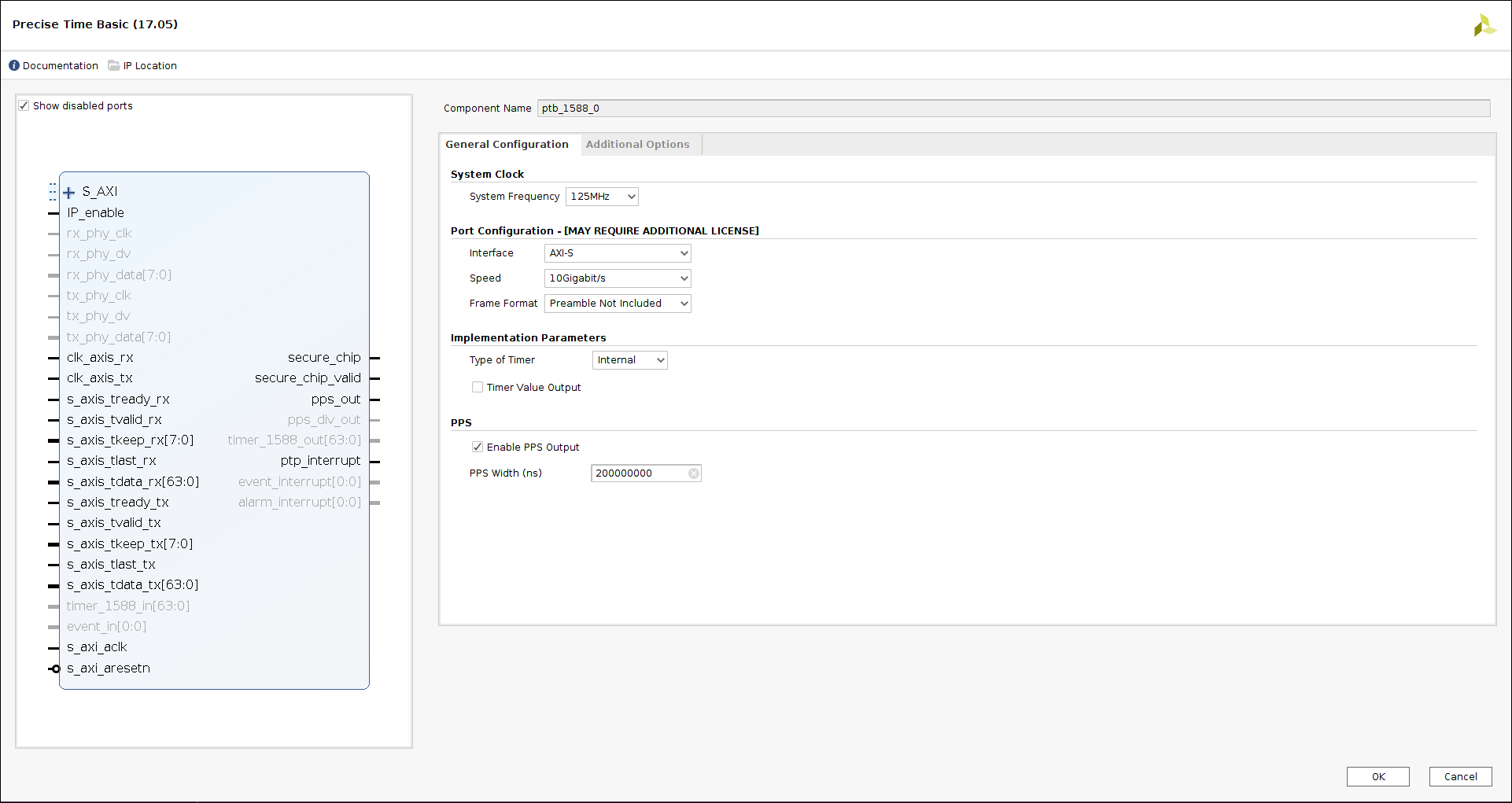

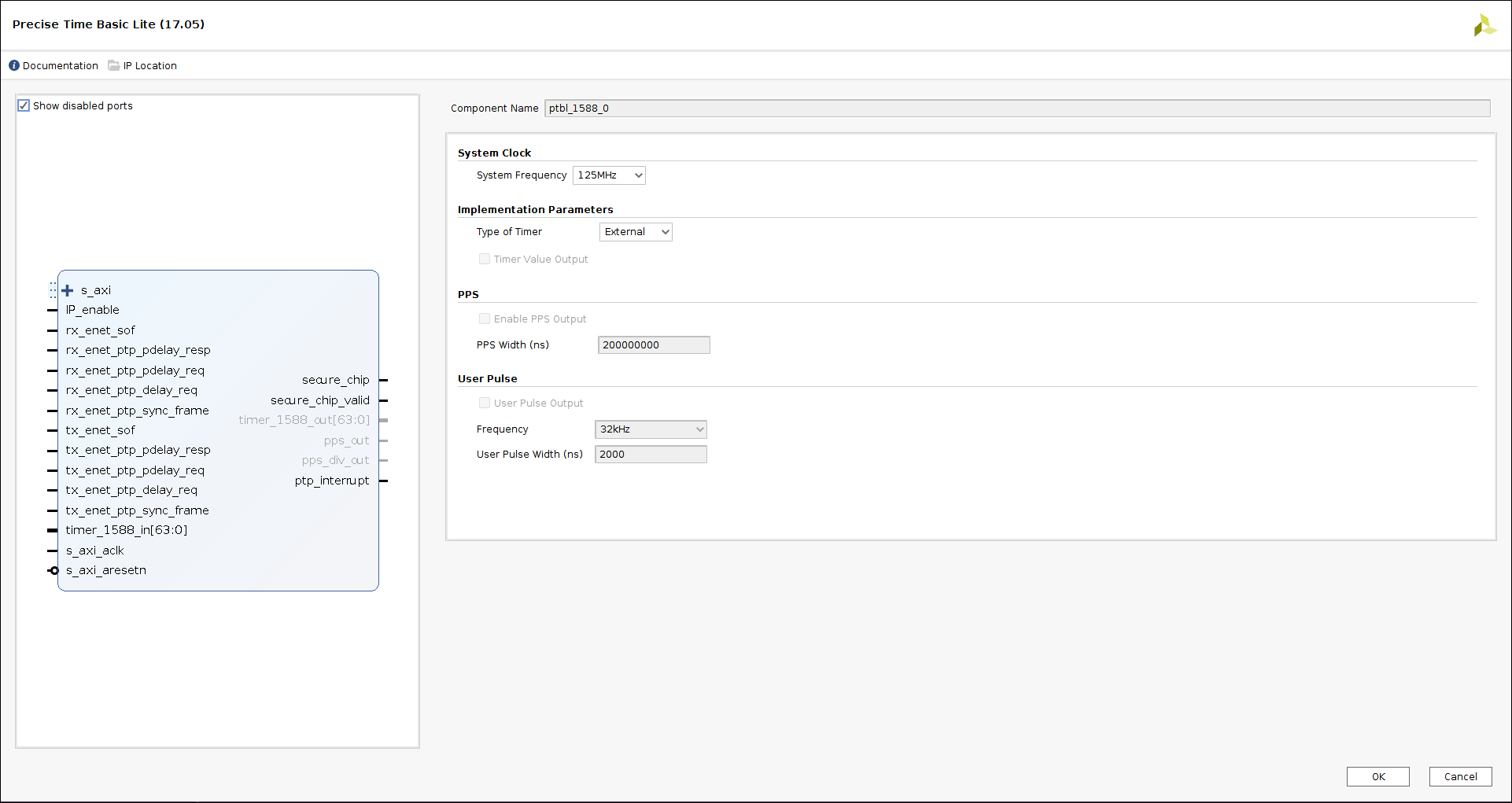

- A hardware Time Stamping Unit (TSU) capable of accurately time stamp IEEE 1588 event messages and to provide an adjustable timer with submicrosecond precision. In fact, two versions of TSU are provided with the PreciseTimeBasic: PTB TSU and PTBLite TSU.

- PTB TSU has been designed to be connected to the Medium Independent Interface ([G]MII), between MAC and PHY, parsing all the Ethernet frames and inspecting which ones are IEEE 1588.

- PTBLite TSU takes advantage of the PTP parser contained in the Zynq GMACs to provide a TSU usingless FPGA resources but with some limitations imposed by the IEEE 1588 hardwired logic on the PS GMAC.

Both versions of TSU can use an internal adjustable timer or take its timer value from another TSU. Thus multiple Ethernet connections can share the same timer or different Ethernet connections may have their individual timer.

- A software PTP Reference Design. SoC-e provides a Linux kernel patch that allow accessing the TSUs using the Linux PTP Hardware Clock (PHC) subsystem. A modified version of the Open Source LinuxPTP software stack with additional features is also provided. Because of its modular design, porting to other operating is feasible.

PreciseTimeBasic can be supported on the following Xilinx FPGA Families:

- 7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

- Versal ACAP

It is designed to be easily integrated in your FPGA designs by taking advantage of the new Xilinx Vivado Tool, that allows to use the IP Cores in a graphical user interface and configure IP parameters in an easy way.

PreciseTimeBasic IP Core key features:

Hardware features:

- 10/100/1000Mbps/AXI-Stream (For 10Gbps/25Gbps) Interfaces supported

- 32 bit seconds / 32 bit nanoseconds counter

- 32 bit subnanosecond frequency adjust

- One Pulse Per Second Output available

- Frequency Selectable Output available (1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz)

- Minimum FPGA resources utilization

- Alarm Generation

- Event Timestamping

Software features:

- Ordinary Clock (Slave & Master) operation

- End-to-End and Peer-to-Peer delay mechanisms support

- Support for PTP on both Layer 2 (Ethernet) and Layer 3 (IPv4) interfaces

- It can be combined with HSR-PRP and ManagedEthernet IP Cores

- VLAN support

- Industrial Profiles: Default, Power, Power-Utility IEC 61850-9-3, IEEE 802.1AS.

- Automotive profile: IEEE 802.1AS general PTP (gPTP) profile.

- Enterprise profile/5G/telecom profiles: G.8265.1, G.8275.1, and G.8275.2.

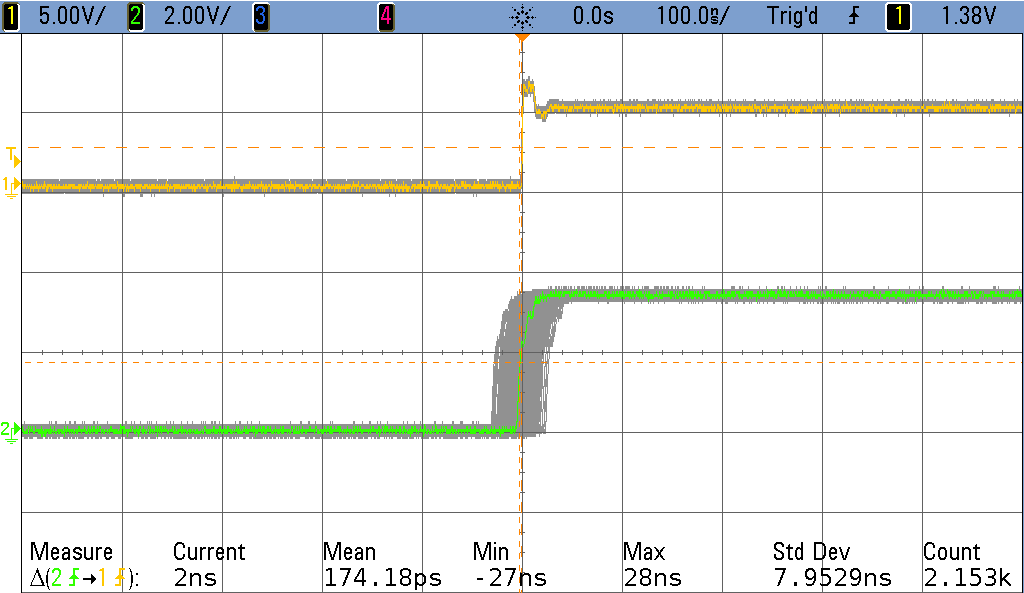

The final accuracy obtained in a IEEE 1588 systems depends on many factors (frequency and quality of the local clock, location of the time stamp in the data chain, etc.). As a reference, next figure shows the measured error between the PPS generated by a Commercial Grandmaster equipment and the PPS generated by a Zedboard Avnet Devopment Platfrom which runs LinuxPTP software stack in the ARM processor and uses the PreciseTimeBasic for hardware assisted timestamping (+/- 50 ns).

Supported boards for the Reference Designs:

- SoC-e SMARTzynq brick (Recommended)

- For other Xilinx/Avnet/SoC-e boards, we can provide a time-limited IP Core for evaluation.