The Sampled Measured Value (SMV or SV) Process Bus concept that was introduced by the IEC 61850-9-2 standard. This standard proposes that the Current and Voltage Transformer (CT, PT) outputs and other signals are digitized at the source and then communicated to those devices using an Ethernet-Based Local Area Network (LAN).

The Sampled Values are transmitted as high speed streams of data set samples encoded in multicast Ethernet frames. The protocol uses a publisher/subscriber model, in which a publisher transmits unacknowledged data to subscribers. As an example, in IEC 61850-9-2 LE profile, the Sampled Values are published at a rate of 4000 frames per second for a grid frequency of 50Hz and 4800 frames per second for 60 Hz.

SoC-e has developed an innovative technology to process massively SMV streams with a deterministic and very low latency taking benefit from parallel hardware processing on FPGAs. All the required functionality has been embedded in a single IP core named SMVsubscriber IP.

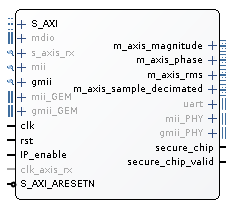

SMVsubscriber analyses incoming traffic and detects IEC 61850-9-2 Sampled Measured Values (SMV) frames. According to several configuration parameters, selected SMV frames are processed, extracting the sampled values of current and voltage for the four phases (A, B, C and N). The IP uses those sampled values to perform the computation of the Discrete Fourier Transform (DFT) to get the angle and magnitude as well as the Root Mean Square (RMS) of each phase. It also provides the samples with the user defined decimation rate.

SMVsubscriber analyses incoming traffic and detects IEC 61850-9-2 Sampled Measured Values (SMV) frames. According to several configuration parameters, selected SMV frames are processed, extracting the sampled values of current and voltage for the four phases (A, B, C and N). The IP uses those sampled values to perform the computation of the Discrete Fourier Transform (DFT) to get the angle and magnitude as well as the Root Mean Square (RMS) of each phase. It also provides the samples with the user defined decimation rate.

SMVsubscriber key features are:

- Layer 2 IEC 61850-9-2 (SMV) frame processing

- High performance implementation of DFT computation module for calculating magnitude and phase of the first harmonic (50 or 60 Hz)

- High performance RMS computation module (up to 1562500 calculations/s)

- Up to 128 simultaneous SMV streams supported (up to 320 streams depending on the process Window configuration)

- Deterministic latency time for full computation of 6us

- Status, configuration and statistic counter registers

- 1000 Mbps AXI-Stream interface for seamless on-chip communications and combination with SoC-e networking IPs (HSR/PRP, Ethernet, TSN)

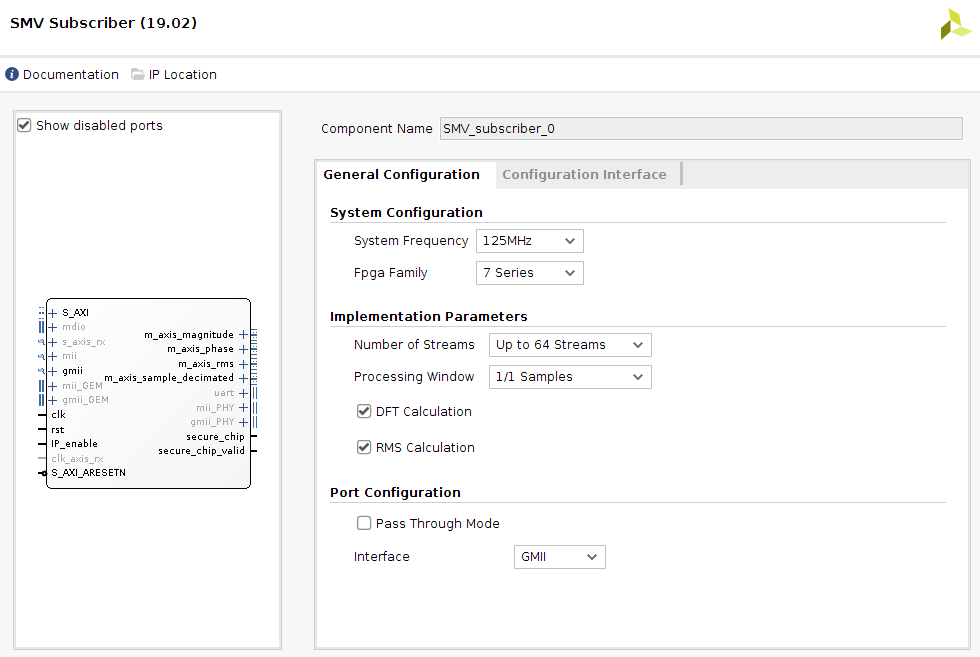

SMVsubscriber allows a flexible and easy customization (GUI interface) to generate the optimum implementation depending on the performance-resources required trade-off. Among other parameters, SMVsubscriber allows configuring:

- The maximum number of streams supported

- The parallelism level of the hardware DFT processing module

- The parallelism level of the Implementable RMS processing module

- The decimation ration for RAW SMV frames sent to higher software applications

- The sample processing rate and window to adjust the frequency for each stream at which the

DFT and RMS are calculated

Supported Xilinx FPGA Families and Evaluation boards

SoC-e SMV IP Core can be deployed in the following Xilinx families. You can find the different Xilinx product tables and selection guides at the following links:

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+(Zynq MPSoC, Kintex, Virtex)

- Versal

For more information: